For non-manifest real-time stream processing applications

# AUTOMATIC PARALLELIZATION of NESTED LOOP PROGRAMS for NON-MANIFEST REAL-TIME STREAM PROCESSING APPLICATIONS

Tjerk Bijlsma

#### Members of the dissertation committee:

Prof.dr.ir. M.J.G. Bekooij University of Twente (first promotor)

**NXP Semiconductors**

Prof.dr.ir. G.J.M. Smit University of Twente (second promotor)

Prof.dr.ir. R. Leupers RWTH Aachen University

Prof.dr.ir. H. Corporaal Eindhoven University of Technology

Dr. T.P. Stefanov Leiden University

Prof.dr.ir. A. Rensink University of Twente

Prof.dr.ir. J.L. Hurink University of Twente

Prof.dr.ir. A.J. Mouthaan University of Twente (chairman)

This work was carried out at NXP Semiconductors in a project of NXP Semiconductors Research. This work contributed to the Center for Telematics and Information Technology (CTIT) research program.

Copyright © 2011 By T. Bijlsma, Oss, The Netherlands.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission by the author.

Cover design by M. Bijlsma. This thesis was printed by Gildeprint, The Netherlands.

ISBN 978-90-365-3173-3 ISSN 1381-3617, No. 11-189 DOI 10.3990/1.9789036531733

#### AUTOMATIC PARALLELIZATION of NESTED LOOP PROGRAMS for NON-MANIFEST REAL-TIME STREAM PROCESSING APPLICATIONS

#### **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof. dr. H. Brinksma,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op vrijdag 1 juli 2011 om 14.45 uur

door

Tjerk Bijlsma

geboren op 23 oktober 1981 te Franeker Dit proefschrift is goedgekeurd door de promotoren:

prof. dr. ir. M. J. G. Bekooij

en

prof. dr. ir. G. J. M. Smit

#### Voorwoord

Dit proefschrift is ontstaan met de hulp, steun en ook afleiding van veel collega's, vrienden en familie. Hiervoor wil ik hen bedanken.

Ik begin met het bedanken van Pierre Jansen, Gerard Smit en Pascal Wolkotte. Tijdens mijn afstuderen bij Pierre heb ik samen met Gerard en Pascal een artikel geschreven. Het onderzoek voor mijn afstudeeropdracht en het schrijven van dit artikel bevielen zo goed dat ik op zoek gegaan ben naar een promotieplek. Via Gerard en Pierre vond ik een mogelijkheid bij Philips Research, wat vrij snel NXP Semiconductors Research werd. Gerard is mijn tweede promotor geworden en heeft mij de afgelopen vier jaar begeleid. Ik wil Gerard en Pierre bedanken voor alle discussies en hun commentaar.

Bij NXP kwam ik in het Hijdra project, waar Marco Bekooij mijn dagelijkse begeleider en later mijn eerste promotor werd. Samen hebben we gewerkt aan het onderzoek voor en de ontwikkeling van de multiprocessor compiler en de parallellisatie tool Omphale. De resultaten hebben we op meerdere conferenties en workshops gepresenteerd. Ik wil Marco bedanken voor alle discussies, inzichten en zijn commentaar waarbij we vaak dankbaar gebruik maakten van de whiteboards die naast de koffieautomaten hingen.

Very important for a promotion are the office mates. Aleksandar Milutinovic and Benny Åkesson, thanks for sharing five different offices with me in the past four years. Furthermore, I want to thank all colleagues and fellow Ph.D. students in the SOC Architectures and Infrastructure group at NXP, especially Maarten Wiggers and Erik Larsson, for the interesting discussions and refreshing coffee brakes. Our multiprocessor compiler would not have been what it currently is, without the contributions of the students Sven Goossens, Stefan Geuns, and Joost Hausmans.

Ik wil ook de collega's in de Computer Architecture for Embedded Systems groep van de Universiteit Twente bedanken. Bedankt voor alle gezellige discussies en voor de bureaus die jullie met me wilden delen terwijl ik Enschede bezocht. De secretaresses Marlous, Thelma en Nicole wil ik bedanken voor alle hulp.

Hiel belangryk binne de freonen en de famylje, sûnder jim' wie ik nea sa fier kommen. Bedankt foar alle belangstelling en ôflieding troch de jierren hinne. Us heit en mem wol ik bedanke, om't se my fan jongs ôf oan steund en motivearre ha mei alles wat ik die. Myn twa broerkes Folkert en Menno wol ik bedanke foar alle ôflieding en gekkichheden, mar ek om't se my altiten holpen ha wêr't se mar koene. Menno, bedankt foar it moaie omslach. Lieme en Aly, bedankt foar al jimme belangstelling en om't ik by jimme altiten wolkom bin, as of't in twadde thús is. Mar boppe al wol ik Dieuwke bedanke foar al har leafde en geduld de ôfrûne jierren.

#### **Abstract**

This thesis is concerned with the automatic parallelization of real-time stream processing applications, such that they can be executed on embedded multiprocessor systems.

Stream processing applications can be encountered in the channel decoding and video decoding domain. These applications typically have real-time requirements. Important trends for stream processing applications are that they become more computational intensive and that they contain more non-manifest conditions and expressions. For non-manifest conditions and expressions, the behavior is unknown at compile time.

Stream processing applications are often executed on multiprocessor systems. Because stream processing applications become more computational intensive, the number of processors in these systems increases. Due to the increasing number of processors, the mapping effort for stream processing applications onto these systems increases. Furthermore, the validation effort for stream processing applications on such systems increases, because the satisfaction of temporal constraints has to be validated for an application that is executed on multiple processors.

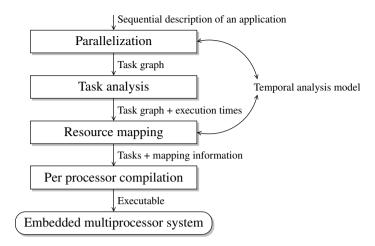

To map stream processing applications onto a multiprocessor system, we use a multiprocessor compiler. We consider multiprocessor compilers that perform automatic parallelization. Otherwise, the user should perform the partitioning of the application manually, which can be time-consuming and error-prone.

For our application domain, we focus on the extraction of function parallelism, because it is often available in stream processing applications. Stream processing applications contain function parallelism, because they are often composed of functions that can be executed independently from each other.

The extraction of parallelism requires the derivation of data dependencies in an application. These data dependencies indicate the execution order of the tasks. If the data dependencies between two statements cannot be determined at compile time, then these statements can often not be executed in parallel.

The parallel execution of tasks requires inter-task communication buffers. Many approaches use first-in-first-out (FIFO) buffers for the inter-task communication. A FIFO buffer supports only one reading and one writing task. However, an application from which parallelism is extracted may contain multiple statements that read from and write into an array. To replace the communication via such an array by inter-task communication, multiple FIFO buffers should be used. It can be difficult to extract a function for a task that determines per array access from which FIFO buffer the value should be read or into which buffer it should be written.

To verify that the temporal constraint of a stream processing application is met, a temporal analysis model should be derived. Such a model should be extracted from an application that contains cyclic data dependencies and non-manifest behavior.

Current parallelization approaches have difficulties with the extraction of function parallelism from stream processing applications. Some of these approaches require applications with manifest behavior and affine index-expressions. For these applications, they can derive data dependencies and insert inter-task communication via FIFO buffers. But, these approaches cannot support stream processing applications with non-manifest loops. Furthermore, current approaches can only extract a temporal analysis model from applications with manifest behavior and without cyclic data dependencies.

To address the issues mentioned above, we present in this thesis an automatic parallelization approach to extract function parallelism from sequential descriptions of real-time stream processing applications. We introduce a language to describe stream processing applications. The key property of this language is that all dependencies can be derived at compile time. In our language we support non-manifest loops, if-statements, and index-expressions. We introduce a new buffer type that can always be used to replace the array communication. This buffer supports multiple reading and writing tasks. Because we can always derive the data dependencies and always replace the array communication by communication via a buffer, we can always extract the available function parallelism. Furthermore, our parallelization approach uses an underlying temporal analysis model, in which we capture the inter-task synchronization. With this analysis model, we can compute system settings and perform optimizations. Our parallelization approach is implemented in a multiprocessor compiler. We evaluated our approach, by extracting parallelism from a WLAN channel decoder application and a JPEG decoder application with our multiprocessor compiler.

# Samenvatting

Dit proefschrift gaat over automatische parallellisatie van realtime stroomverwerkende applicaties, opdat ze uitgevoerd kunnen worden op een embedded systeem met meerdere rekenkernen.

Stroomverwerkende applicaties komen vaak voor in het kanaaldecoderings- en videodecoderingsdomein en verwerken een continue stroom van waardes. Dit soort applicaties hebben meestal realtime eisen. Belangrijke trends voor stroomverwerkende applicaties zijn dat ze berekeningsintensiever worden en dat ze steeds meer non-manifeste condities en expressies bevatten. Bij non-manifest condities en expressies is het gedrag onbekend gedurende de compilatie.

Stroomverwerkende applicaties worden vaak uitgevoerd op systemen met meerdere rekenkernen. Omdat stroomverwerkende applicaties rekenintensiever worden, neemt het aantal rekenkernen in deze systemen toe. Door het toenemende aantal rekenkernen wordt het steeds moeilijker om stroomverwerkende applicaties op deze systemen af te beelden. Ook wordt het moeilijker om het gedrag van de stroomverwerkende applicaties te valideren voor systemen met meerdere rekenkernen, omdat voor een applicatie die door meerdere rekenkernen uitgevoerd wordt, gevalideerd moet worden dat aan de tijd gerelateerd eisen voldaan wordt.

Om stroomverwerkende applicaties af te beelden op een systeem met meerdere rekenkernen gebruiken we een multiprocessorcompiler. We beschouwen multiprocessorcompilers die automatische parallellisatie uitvoeren. Anders zou de gebruiker het opdelen van de applicatie handmatig uit moeten voeren, wat tijd rovend en foutgevoelig is.

Voor ons applicatiedomein richten we ons op het afleiden van functieparallellisme, omdat dit vaak beschikbaar is in stroomverwerkende applicaties. Stroomverwerkende applicaties bevatten functieparallellisme, omdat ze vaak zijn opgebouwd uit functies die onafhankelijk van elkaar uitgevoerd kunnen worden.

Het afleiden van parallellisme vereist dat de data-afhankelijkheden in een applicatie bepaald worden. Deze data-afhankelijkheden geven de volgorde aan waarin de taken uitgevoerd moeten worden. Als de data-afhankelijkheden tussen twee statements niet bepaald kunnen worden gedurende de compilatie, dan kunnen deze statements niet parallel uitgevoerd worden.

Het parallel uitvoeren van taken vereist buffers voor de communicatie tussen de taken. Veel aanpakken gebruiken first-in-first-out (FIFO) buffers, waarvoor geldt dat de eerst geschreven waarde als eerste gelezen wordt. Een FIFO buffer ondersteunt slechts één enkele lezende en schrijvende taak. Een applicatie waarvan parallellisme afgeleid wordt, kan meerdere statements bevatten die schrijven in of lezen uit een array. Het vervangen van de communicatie via deze array door communicatie tussen taken, vereist het gebruik van meerdere FIFO buffers. Het kan moeilijk zijn om een functie af te leiden, die per schrijf– of leesactie voor een array bepaalt in welke FIFO buffer de waarde geschreven of gelezen zou moeten worden.

Om te verifiëren dat aan de tijd gerelateerde eisen van een stroomverwerkende applicatie voldaan wordt, moeten we een temporeel analysemodel afleiden. Dit model moet afgeleid kunnen worden van een applicatie die cyclische data-afhankelijkheden en nonmanifest gedrag bevat.

De huidige parallellisatie-aanpakken hebben moeite met het afleiden van functieparallellisme van stroomverwerkende applicaties. Sommige van deze aanpakken vereisen applicaties met manifest gedrag en affine indexexpressies. Voor deze applicaties kunnen ze de data-afhankelijkheden afleiden en communicatie tussen de taken invoegen via FIFO buffers. Deze aanpakken kunnen stroomverwerkende applicaties met nonmanifeste lussen niet ondersteunen. Verder kunnen de huidige aanpakken alleen een temporeel analysemodel afleiden van applicaties met manifest gedrag en zonder cyclische data-afhankelijkheden.

De boven genoemde problemen beschouwende, presenteren wij in dit proefschrift een automatische parallellisatie-aanpak om functieparallellisme af te leiden van sequentiële beschrijvingen van realtime stroomverwerkende applicaties. We introduceren een taal om stroomverwerkende applicaties te beschrijven. De kern eigenschap van deze taal is dat alle data-afhankelijkheden bepaald kunnen worden gedurende de compilatie. In onze taal ondersteunen we non-manifeste lussen, if-statements, en indexexpressies. We introduceren een nieuw buffertype dat altijd toegepast kan worden om de communicatie via een array te vervangen. Dit buffertype ondersteunt meerdere schrijvende en lezende taken. Omdat we altijd de data-afhankelijkheden af kunnen leiden en altijd de array communicatie kunnen vervangen door communicatie via een buffer, kunnen we altijd het beschikbare functieparallellisme afleiden. Onze parallellisatie-aanpak gebruikt een onderliggend temporeel analysemodel, waarin we de synchronisatie tussen de taken weergeven. Met dit analysemodel kunnen we instellingen voor een systeem met meerdere rekenkernen berekenen en optimalisaties uitvoeren. Onze parallellisatieaanpak is geïmplementeerd in een multiprocessorcompiler. We hebben onze aanpak geëvalueerd door met onze multiprocessorcompiler parallelisme af te leiden van een WLAN-kanaaldecodeerapplicatie en een JPEG-decodeerapplicatie.

# Contents

| I | Intr | oduction                             | 1  |

|---|------|--------------------------------------|----|

|   | 1.1  | Stream processing application domain | 2  |

|   | 1.2  | Embedded multiprocessor system       | 3  |

|   | 1.3  | Multiprocessor compiler              | 4  |

|   | 1.4  | Problem statement                    | 8  |

|   | 1.5  | Contributions                        | 9  |

|   | 1.6  | Justification of the approach        | 9  |

|   | 1.7  | Outline                              | 10 |

| 2 | Rela | nted work                            | 11 |

|   | 2.1  | Sequential programming languages     | 12 |

|   | 2.2  | Parallelization tools                | 14 |

|   | 2.3  | Parallel programming languages       | 17 |

|   | 2.4  | Temporal analysis models             | 19 |

|   | 2.5  | Conclusion                           | 20 |

| 3 | Mul  | tiprocessor compiler                 | 23 |

|   | 3.1  | Multiprocessor compiler overview     | 23 |

|   | 3.2  |                                      | 26 |

|   | 3.3  | Conclusions                          | 30 |

| 4 | Dep  | endency graph extraction             | 31 |

|   | 4.1  | Data dependencies                    | 32 |

|   | 4.2  | Data dependency analysis             | 33 |

|   | 4.3  |                                      | 37 |

|   | 4.4  | Dependency graph                     | 44 |

xii CONTENTS

|    | 4.5<br>4.6 | Access pattern extraction                      | 48<br>50 |  |  |  |

|----|------------|------------------------------------------------|----------|--|--|--|

| 5  | Inte       | r-task communication buffers                   | 51       |  |  |  |

|    | 5.1        | Memory consistency model                       | 52       |  |  |  |

|    | 5.2        | FIFO communication issues                      | 55       |  |  |  |

|    | 5.3        | Buffer with sliding windows                    | 59       |  |  |  |

|    | 5.4        | Buffer with overlapping windows                | 64       |  |  |  |

|    | 5.5        | Conclusion                                     | 69       |  |  |  |

| 6  | Con        | nmunication and synchronization insertion      | 71       |  |  |  |

|    | 6.1        | Generic template                               | 72       |  |  |  |

|    | 6.2        | Manifest access patterns                       | 74       |  |  |  |

|    | 6.3        | Non-manifest access patterns                   | 85       |  |  |  |

|    | 6.4        | Stream processing                              | 91       |  |  |  |

|    | 6.5        | Access types                                   | 94       |  |  |  |

|    | 6.6        | Conclusion                                     | 97       |  |  |  |

| 7  | Tem        | Temporal analysis model                        |          |  |  |  |

|    | 7.1        | Shortcomings of local analysis                 | 100      |  |  |  |

|    | 7.2        | The CSDF analysis model                        | 104      |  |  |  |

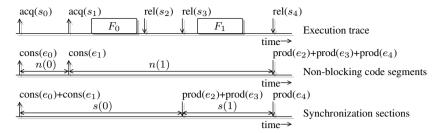

|    | 7.3        | Synchronization sections                       | 106      |  |  |  |

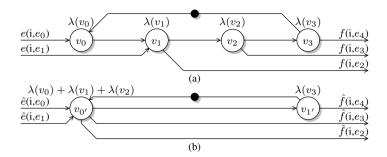

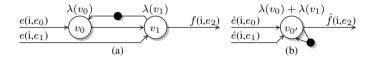

|    | 7.4        | Modeling manifest synchronization behavior     | 114      |  |  |  |

|    | 7.5        | Modeling non-manifest synchronization behavior | 123      |  |  |  |

|    | 7.6        | Conclusion                                     | 124      |  |  |  |

| 8  | Case       | e studies                                      | 125      |  |  |  |

|    | 8.1        | WLAN channel decoder                           | 126      |  |  |  |

|    | 8.2        | JPEG decoder                                   | 132      |  |  |  |

|    | 8.3        | Conclusion                                     | 137      |  |  |  |

| 9  | Conclusion |                                                |          |  |  |  |

|    | 9.1        | Summary                                        | 140      |  |  |  |

|    | 9.2        | Contributions                                  | 142      |  |  |  |

|    | 9.3        | Future work                                    | 142      |  |  |  |

| Bi | bliogi     | raphy                                          | 145      |  |  |  |

| Li | st of p    | publications                                   | 155      |  |  |  |

# CHAPTER 1

# Introduction

This thesis is concerned with the automatic parallelization of real-time stream processing applications, such that they can be executed on embedded multiprocessor systems. These stream processing applications process streams of values, contain if-statements and while-loops with conditions that depend upon input values from the stream, and often have temporal requirements. State-of-the-art automatic parallelization approaches can extract parallelism from such applications, but have difficulties supporting if-statements and while-loops. Furthermore, these approaches have difficulties with the extraction of a temporal analysis model, which is required for the verification of temporal constraints.

In this thesis, we will present a new parallelization approach for stream processing applications. We will introduce a new language that supports if-statements and while-loops, such that we can always analyze the dependencies. We introduce a new buffer type that we can always use to replace the communication via arrays, such that parallelism can always be extracted. Besides a task graph, we extract an analysis model from the synchronization behavior between the tasks in the task graph. With this analysis model, the temporal requirements can be verified and even optimizations can be computed for the task graph. This parallelization approach is part of a multiprocessor compiler with which we demonstrated the extraction of parallelism given industrial relevant stream processing applications.

The organization of this chapter is as follows. In section 1.1, we will first examine the characteristics of stream processing applications, followed by a discussion on the targeted embedded multiprocessor systems in Section 1.2. For the multiprocessor compilers that compiles stream processing applications for multiprocessor systems, we will discuss the input format and the state-of-the-art automatic parallelization approaches, in Section 1.3. Considering the requirements and the state-of-the-art for automatic paral-

lelization, Section 1.4 presents our problem statement. Subsequently, we present our key contributions in section 1.5. Section 1.6 gives a justification of our approach. An outline of the remainder of the thesis is presented in Section 1.7.

### 1.1 Stream processing application domain

In this thesis, we consider so called stream processing applications that process endless streams of input values. Stream processing applications are encountered in the channel decoding and the video processing domain and are therefore considered interesting by NXP semiconductors, for which this research was partly conducted.

A stream processing application processes an endless stream of input values. Therefore, these applications typically contain an *endless loop* in which these values are read and processed.

The behavior of a stream processing application can depend upon its input values, because it may contain an if-statement or a while-loop with a condition for which the result of its expression depends upon input values from the stream. In addition, the result of an index-expression used to access array elements may also depend upon input values. The result of such a condition or index-expression cannot be evaluated at compile time and they are therefore called *non-manifest*. In contrast, for a manifest condition or index-expression the result can be evaluated at compile time. We will call if-statements and while-loops with conditions that cannot be evaluated at compile time *non-manifest if-statements* and *non-manifest loops*. Index-expressions that cannot be evaluated at compile time will be called *non-manifest index-expressions*. We will call the combination of non-manifest loops, if-statements, and index-expressions *non-manifest statements*.

For stream processing applications, we identify two trends: 1) they become more computational intensive and 2) they tend to contain an increasing number of non-manifest conditions and expressions. The computational requirements for stream processing applications increase, due to the increased quantity and quality of the media that the users desire. For channel decoding and video processing applications, this often implies an increase in bit rate, which requires more computations to be performed for a single value from the input stream. Stream processing applications tend to contain more non-manifest conditions and expressions, such that they can adapt to changes in their environment.

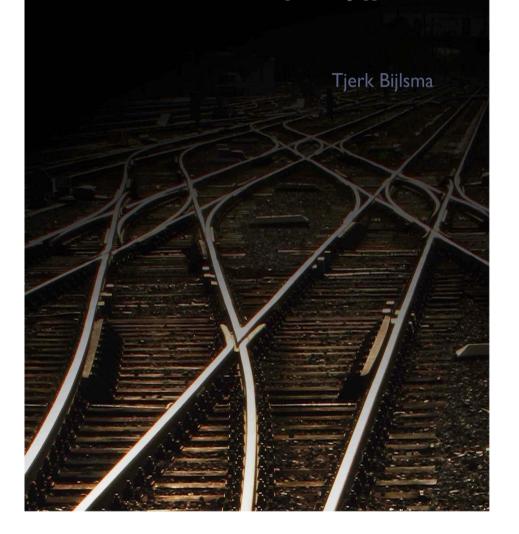

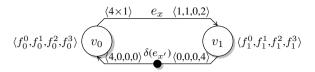

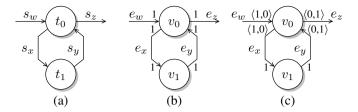

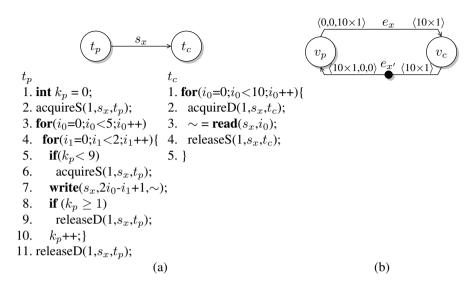

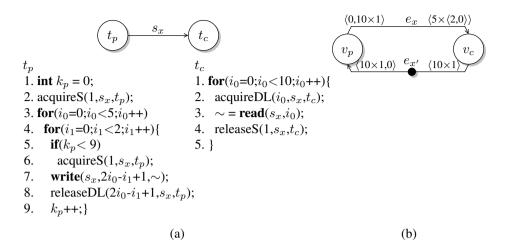

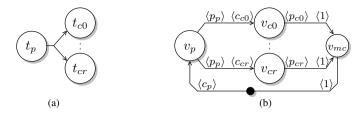

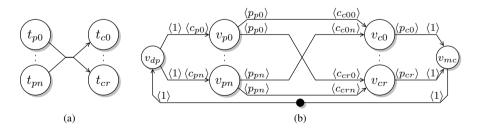

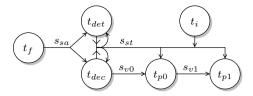

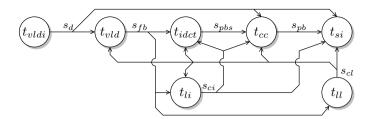

A channel decoder performs stream processing and contains non-manifest conditions and has therefore been an important driver application behind this work. Figure 1.1 depicts a channel decoder. This channel decoder processes an endless stream of input values in the form of samples that it receives in buffer  $s_b$  from the radio front-end task  $t_f$ . The channel decoder either decodes by executing the tasks  $t_{dec}$ ,  $t_{p0}$ , and  $t_{p1}$  or detects by executing  $t_{det}$ . Depending on the state of the previous iteration stored in buffer  $t_c$ , the tasks  $t_{dec}$ ,  $t_{p0}$ ,  $t_{p1}$ , and  $t_{det}$  determine if they have to execute.

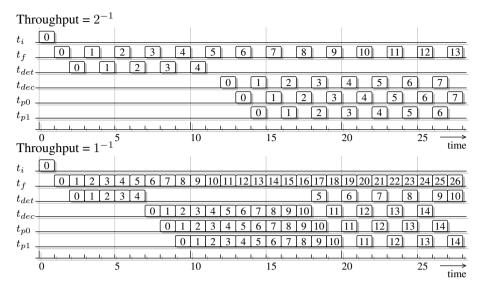

Often, a stream processing application has a real-time constraint in the form of a *temporal requirement*. Such a requirement typically comes in the form of a throughput constraint. Channel decoders typically have a throughput constraint, such that it is guaranteed that the input values are consumed at a fixed rate. This prevents the buffers at

Figure 1.1: A task graph of a channel decoder that performs stream processing

the input of the channel decoder from overflowing, such that no value will be lost. Note that a throughput requirement does not restrict the end-to-end latency of an application. Therefore, the application can be pipelined to meet the throughput requirement.

# 1.2 Embedded multiprocessor system

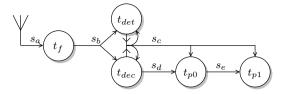

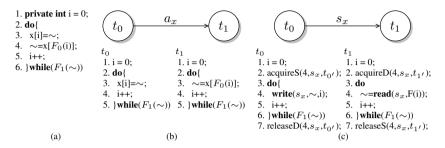

To execute a stream processing application, we will use an embedded multiprocessor system. These systems typically contain multiple processors and memories. We will program an embedded multiprocessor system with a so called shared address space programming model that allows tasks to communicate by writing in and reading from shared memory locations.

For embedded systems, we identify two trends: 1) the numbers of processors on a chip is increasing, and 2) multiple memories are used on a single chip. The first trend indicates that instead of increasing the frequency of a processor, multiple processors are provided, such that the total amount of processing power is increased. Furthermore, due to the increasing number of processors, providing a single physical shared memory on the chip would become a performance bottleneck. Therefore, the trend is to provide multiple memories on a chip, which results in the processors having a non-uniform memory access (NUMA) latency. Often, some of these memories are assigned as a local memory to some processors, which typically implies that the memory cannot be read by all processors on the chip.

To program an embedded multiprocessors system, we will consider a *shared address space* programming model [CGS99] in which tasks can communicate and synchronize via shared locations in the memories. This programming model comes with some additional communication overhead, because to write at a memory location, the address of the location has to be communicated along with the value to be written. The clear benefit of this programming model is that it simplifies the mapping of tasks to processors, because the memory accesses of tasks are independent from the processor the task is mapped to. Each processor will use the same address for a shared location, such that it is not necessary to tailor the code of a task for its processor.

Figure 1.2 depicts two multiprocessor systems with a *physical shared address space*, on top of which the shared address space programming model can easily be used. In these architectures, the tasks can perform communication and synchronization via the shared memory. Note, that physical shared address space architectures can contain local

Figure 1.2: Examples of embedded multiprocessor systems with a physical shared address space

memories that cannot be read by all processors. If a task needs to read from locations in such a local memory, it should be executed by a processor that can also read these locations.

# 1.3 Multiprocessor compiler

A multiprocessor compiler maps a stream processing application onto an embedded multiprocessor system. Depending upon its input, the compiler has to perform automatic parallelization. We will discuss the consequence of starting from a parallel or a sequential description of an application. Subsequently, we examine state-of-the-art automatic parallelization approaches for stream processing applications.

#### 1.3.1 Multiprocessor compiler input

A multiprocessor compiler can either start from a parallel or sequential description of an application. By starting from a sequential description, a user can provide a compact description of the application, without the need to partition the application manually. In addition, it is beneficial that the parallelization front-end of the compiler automatically extracts an analysis model, such that temporal requirements can be validated.

For the execution of stream processing applications on embedded multiprocessor systems, the trends of the applications and the systems have two clear implications: the mapping effort of applications onto the multiprocessor system increases and the validation effort of the mapped applications increases [MP03]. The *mapping effort* of a stream processing application onto a multiprocessor system increases, because the required processing power for the application can only be satisfied by using multiple processors. Therefore, the application has to be partitioned into multiple tasks that can be executed in parallel on different processors. Because these tasks are executed on different processors, they should perform inter-task communication via shared memory. The *validation effort* increases, because the satisfaction of the temporal requirements has to be validated for a stream processing application that is executed over multiple processors that share resources.

To execute a stream processing application on an embedded multiprocessor system, a multiprocessor compiler is required. This compiler should compute a mapping of tasks

to processors and allocate memories to tasks, such that the temporal requirements of the application are satisfied.

A multiprocessor compiler can start from a parallel description or a sequential description of the stream processing application. A sequential description of an application specifies the execution order of the statements, such that it does not require synchronization statements. A parallel description does not completely specify the execution order, such that it must contain synchronization statements. By starting from a *parallel description*, the user has to manually partition the application and can also optimize this description. Starting from a parallel description simplifies the front-end of the compiler, because it does not have to extract parallelism. A drawback of this approach is that the user has to partition the application manually, which can be time-consuming and errorprone. The granularity of the tasks in such a manual partitioning of an application is often optimized for a specific multiprocessor system. Furthermore, such a description typically requires manual annotations of the identified tasks, which requires the user to have expert knowledge of the system.

We will start from a *sequential description* of an application from which the compiler automatically extracts parallelism. This requires automatic parallelization. We define automatic parallelization as the identification of tasks and the insertion of inter-task communication and synchronization statements. Therefore, we derive the dependencies in a sequential description, such that tasks can be identified and the array communication for which these dependencies have been derived can be replaced by inter-task communication and synchronization statements. Due to the automatic parallelization, a compact sequential description of the application can be given as input by a user. Such a compact sequential description is typically easy to debug and does not require the user to have expert knowledge of the system. Therefore, we think it is desirable that the front-end of a multiprocessor compiler performs automatic parallelization.

To verify that the temporal constraints of a stream processing application are satisfied, either a corresponding analysis model is required or the constraints should be verified by iterative validation. Verification by iteratively executing the application is time consuming and can in general not guarantee that the temporal constraint will always be satisfied, due to the resource sharing between the processors. An analysis model can be used to guarantee the temporal constraints to be satisfied and can also be used to compute the required resources.

For a compiler, a temporal analysis model of an application can be provided as an input, or can be automatically extracted. Providing an analysis model as *input*, requires the user to describe the synchronization behavior of the parallelized stream processing application, which requires expert knowledge of both the used model and the partitioned application. Furthermore, manually describing this synchronization behavior is errorprone and time consuming. It is beneficial that such an analysis model is *automatically extracted*, such that it corresponds to the parallel description of the application.

#### 1.3.2 Automatic parallelization

In this thesis, we will focus on automatic parallelization for stream processing applications that have temporal requirements.

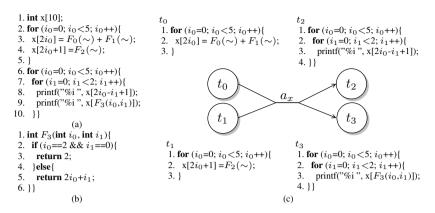

To exploit the parallel execution of the processors in a multiprocessor system, two types of parallelism can be identified: function and data parallelism [CGS99, ALSU06]. For *data parallelism*, typically independent loop-iterations are identified, where each iteration is executed on a different processor, resulting in load balancing of the computations and a reduced synchronization overhead. However, the drawback is that there are often dependencies between loop iterations and after executing the loop iterations, the results need to be combined, which may require additional control-statements and synchronization.

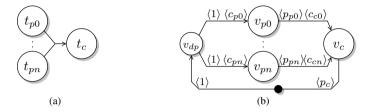

We chose to focus on *function parallelism*, for which a task is created from each function call in the code. Function parallelism can often be extracted from stream processing applications, if they are composed of functions that can be executed independently from each other, as shown by our driver application in Figure 1.1. The main reason to extract function parallelism is that the execution of a stream processing application can be pipelined, such that potentially its throughput can be increased.

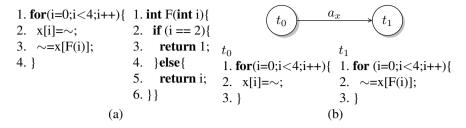

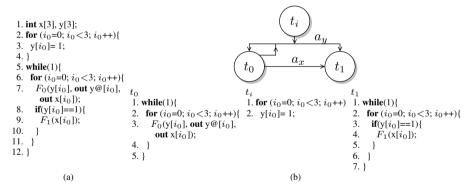

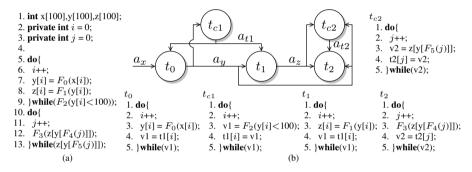

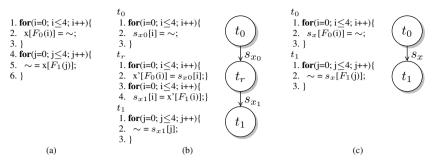

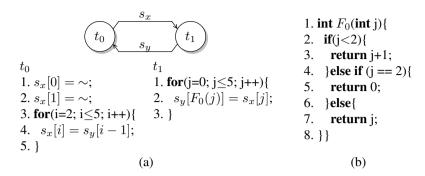

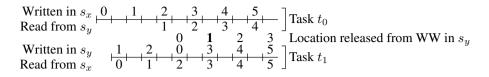

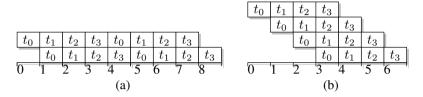

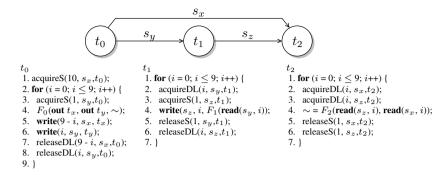

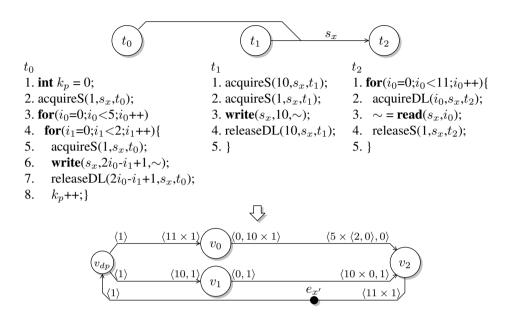

A task graph is extracted from the sequential description of a stream processing application. The sequential description of such an application is often in the form of a nested loop program (NLP), where the bodies of the loops contain assignment-statements with function calls. In an NLP, typically the assignment-statements read from and write into arrays. A task graph is extracted by creating a task from each assignment-statement. These tasks share dependencies via the arrays that they write and read.

To execute the tasks from the task graph in parallel, they have to be extended to use the programming model of the target multiprocessor system. The array communication of the NLP is replaced by inter-task communication via buffers. Synchronization statements are inserted into the tasks, such that the dependencies between the tasks are maintained. This ensures that values are written before they are read.

We have identified two state-of-the-art parallelization approaches for stream processing applications. The Compaan/PN approach [MNS10, Ste04, TKD02, TKD04a, TKD04b, VNS07] extracts function parallelism from NLPs. Therefore, each assignment-statement is executed in a separate task. Sprint [CDVS07] is the second state-of-the-art approach, which extracts parallelism from annotated C code.

The Compaan/PN approach extracts parallelism from affine NLPs and inserts first-infirst-out (FIFO) buffers for the inter-task communication. An *affine* NLP only contains index-expressions that are a summation of variables multiplied by constants plus an optional constant, e.g. 3i+j-4. The expressions for the bounds of the for-loops may contain parameters. The value of such a parameter can be unknown at compile time, but it will not change during the execution of the for-loop. Due to the affine index-expressions, exact data dependencies can be extracted [Fea91], such that the NLP can be transformed into single assignment (SA) form. For an NLP in SA form, a location in an array is written at most once during an execution of the NLP. Inter-task communication via FIFO buffers can be inserted into such an NLP.

In [Ste04] the Compaan/PN approach is extended to extract parallelism from weakly dynamic NLPs. A weakly dynamic NLP may contain non-manifest if-statements in combination with manifest for-loops. A task that is extracted from an assignment-statement in the body of a non-manifest if-statement, has to perform inter-task communication via special FIFO buffers that contain controllers for reading and writing. These controllers are aware of the exact execution schedule of the tasks. The Compaan/PN approach does not support the extraction of parallelism from non-manifest loops in stream processing applications with arbitrary index-expressions.

While this thesis was written, the Compaan/PN approach has been extended to support weakly dynamic NLPs with non-manifest for-loops [NNS10]. However, this extension does still not support the extraction of parallelism from non-manifest while-loops in stream processing applications with non-affine index-expressions.

The Sprint approach extracts parallelism from annotated C code, but requires user input for non-manifest loops or if-statements. This approach can insert FIFO buffers for dependencies between tasks that it can analyze. If the dependencies cannot be analyzed, due to for example non-manifest loops or if-statements, the user should manually insert synchronization and communication statements. Manual insertion of synchronization statements can be error-prone and can lead to hard to debug race-conditions [AB09].

Besides the extraction of a task graph, an analysis model is required, such that temporal requirements can be verified. For the Compaan/PN approach, methods exist to extract an analysis model [HT07, MNS10], but these are only applicable for acyclic task graphs for which they can verify the performance, instead of computing the required resources to meet the temporal constraint. In addition, both approaches cannot capture the non-manifest behavior of our driver application in an analysis model.

Table 1.1 depicts the capabilities of the discussed state-of-the-art approaches and the requirements that we identified for the extraction of parallelism from stream processing applications. To extract parallelism from stream processing applications, the *Compaan/PN* approach supports affine index-expressions and non-manifest if-statements and for-loops with non-manifest upper and lower bounds. This approach can only extract an analysis model from a manifest acyclic task graph. The *Sprint* approach requires user input, if non-manifest expressions are encountered that cannot be analyzed and does not extract an analysis model. For the parallelization of stream processing applications, the support of non-manifest index-expressions is desirable and for non-manifest loops and if-statements a must, as illustrated by our driver application in Figure 1.1. Support of parameterization can be desirable, because this can result in a more efficient task graph. The

| Table 1.1: Automatic parallelization a | pproaches comp | ared to the idei | itified requireme | ents |

|----------------------------------------|----------------|------------------|-------------------|------|

| Non-manifest                           | Non-manifest   | Parameterization | Temporal          |      |

|                                | Non-manifest index-expressions | Non-manifest control-statements | Parameterization | Temporal analysis model  |

|--------------------------------|--------------------------------|---------------------------------|------------------|--------------------------|

| Compaan/PN                     | Affine                         | If-statements and for-loops     | Yes              | Manifest<br>acyclic NLPs |

| Sprint                         | User input                     | User input                      | No               | None                     |

| Required for stream processing | Desirable                      | Loops and if-statements         | Desirable        | Must                     |

extraction of an analysis model is a must, because it is required to validate the temporal requirements of the application.

#### 1.4 Problem statement

The problem addressed in this thesis is to extract a task graph from the NLP of a stream processing application that may contain non-manifest if-statements, loops, and index-expressions and the extraction of a temporal analysis model from this task graph, such that we can guarantee that the temporal constraints of the stream processing application are satisfied and that this task graph can be executed on an embedded multiprocessor system.

The first part of the problem, is the extraction of parallelism from the NLP of an application. Before a task can be created from each assignment-statement, the dependencies between these tasks should be identified. These dependencies indicate the execution order of the tasks, such that values shared between the tasks will be written before they will be read. If the dependencies between the tasks cannot be analyzed, the execution of the tasks cannot be pipelined. Furthermore, if there are dependencies that may point to any location in memory, the local memories in a multiprocessor system cannot be used, because these cannot be read from each processor.

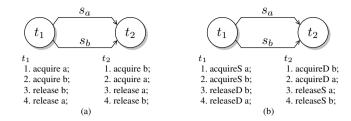

To execute the tasks from a task graph on a multiprocessor system, the communication via arrays in an NLP should be replaced by communication via buffers. A lot of approaches replace array communication by FIFO buffers [CCS+08, CDVS07, DHRA06, RFGEL08, TKD04b, VNS07], but this may introduce the so called buffer selection problem and reordering problem. If multiple tasks read from and write into an array and this array has to be replaced by multiple FIFO buffers, the *buffer selection problem* occurs. Conditions have to be extracted and added to the tasks. These conditions determine if values have to be written in or read from the FIFO buffers. The buffer selection problem will be discussed in detail in Section 5.2.3. If a FIFO buffer is applied for an array that has different access patterns for reading and writing, the *reordering problem* occurs. Values are read from a FIFO buffer in the order that they are written into it. If the writing task writes its values sequentially into the FIFO buffer, the reading task requires a reordering task and reorder memory, to read the locations in the order of its access pattern. The reordering problem will be discussed in detail in Section 5.2.2.

The third problem is the extraction of a temporal analysis model from the synchronization behavior of the task graph, such that the temporal requirements can be verified. The extracted model should be temporally conservative, which means that the modeled events do not occur earlier as they occur in the task graph, in order to give guarantees for the temporal behavior. Furthermore, these events might occur in non-manifest if-statements or non-manifest loops, which should be modeled conservatively.

9

#### 1.5 Contributions

Our main contribution is the introduction of a new automatic parallelization approach, for stream processing applications that are described by NLPs. We defined a new language that supports non-manifest statements and from which we can always extract the dependencies. For this language, we introduced a kind of SA form that we use as a requirement for the description of our applications. We can always extract parallelism, because we introduced a new buffer type that can always be used to replace the array communication from which the dependencies have been derived. We can extract a temporal analysis model from the synchronization between the tasks in the task graph, by conservatively modeling this synchronization.

In more detail, our contributions are:

- 1. The introduction of a new language that supports non-manifest statements to describe stream processing applications, such that we can always extract data dependencies and function parallelism (Chapter 4).

- 2. We can always extract parallelism and guarantee deadlock-free execution, because we introduce two new buffer types that support multiple reading and writing tasks and non-manifest access patterns (Chapter 5). The first buffer type can always be applied, because it can handle latency critical cyclic data dependencies, and the other has a low synchronization overhead.

- 3. We can extract a temporal analysis model from the inter-task synchronization of stream processing applications, except for some non-manifest latency critical cyclic data dependencies. The used buffer types and the inserted inter-task synchronization enable the extraction of a temporal analysis model. With the extracted analysis model, we can guarantee satisfaction of the temporal requirements and perform optimizations (Chapter 7).

- 4. Our parallelization techniques have been integrated in a multiprocessor compiler for stream processing applications, with which we extracted parallelism from industrial relevant applications (Chapter 3 and 8).

# 1.6 Justification of the approach

The automatic parallelization approach presented in this thesis, has been constructed using a bottom-up approach. We used this approach, because it allowed us to present solutions during the development of the multiprocessor compiler.

Due to the bottom-up approach, we defined our own Omphale input language (OIL) for the compiler. This language has been generalized step by step. At each point during development, we could analyze all dependencies in an application and therefore extract parallelism from OIL, because we had strict control of the semantics and statements supported by our language. Backward compatibility with the semantics of existing languages was considered less important.

During the development of the compiler, the addition of new statements and semantics to OIL has triggered generalizations for the buffer types. Furthermore, modeling techniques were defined, such that a conservative analysis model could be extracted and resource requirements could be computed.

#### 1.7 Outline

The organization of this thesis is as follows. We will start with discussing related automatic parallelization approaches. With this discussion, we will highlight our contributions in relation to existing work. The next chapter will present an overview of our multiprocessor compiler for stream processing applications, which relates to contribution 4. This compiler accepts a stream processing application described sequentially in OIL together with a temporal requirement and returns an executable for our multiprocessor system. After the overview, we will discuss our automatic parallelization approach in detail. First, we discuss the dependency analysis, the syntax, and the semantics of OIL, which corresponds to contribution 1. From an application described in OIL, we can always extract a dependency graph. To replace the array communication from which these dependencies were derived by buffers, two new buffer types are introduced, as claimed in contribution 2. We will present templates that define the placement of synchronization and communication statements for these buffers into the tasks, such that the dependency graph is transformed into a task graph. From the synchronization behavior between the tasks in this task graph a temporal analysis model can be extracted, corresponding to contribution 3. We can use this analysis model to validate temporal requirements for the task graph, or even to compute optimizations. With the presented automatic parallelization approach, two case studies have been performed to illustrate its possibilities, this partly relates to contribution 4. Amongst others, the parallelization of a WLAN channel decoder is demonstrated for which we can compute buffer capacities that maximize the overlap in task executions.

The outline of this thesis is as follows. Chapter 2 discusses the related automatic parallelization approaches. Subsequently, an overview of our multiprocessor compiler is given in Chapter 3. In Chapter 4, we discusses the dependency analysis and the extraction of a dependency graph from OIL. To replace the communication via arrays in the dependency graph, Chapter 5 introduces two buffer types. The insertion of statements into the tasks to use these buffers is presented in Chapter 6, which results in a task graph. The extraction of a conservative analysis model from such a task graph is the last step for our automatic parallelization approach and is presented in Chapter 7. Chapter 8 presents an industrial relevant case study that we use to evaluate our parallelization tool. In Chapter 9, we will present our conclusions.

# CHAPTER 2

#### Related work

Abstract - This chapter examines related parallelization approaches, such that we can highlight the differences with our approach. We examine sequential programming languages that can be used as input, parallelization tools, parallel programming languages that can be used as output, and temporal analysis models.

In this chapter, we will highlight the differences between our automatic parallelization approach and related approaches. We will consider four issues: the used sequential programming language to describe input applications, the used parallelization tool, the used temporal analysis model, and the used parallel programming language to describe the task graphs that can be extracted by parallelization tools.

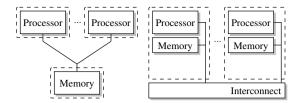

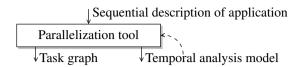

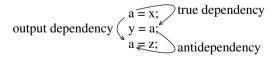

What a parallelization tool carries out is depicted in Figure 2.1. A parallelization tool accepts an application described in a sequential programming language as input and returns a task graph described in a parallel programming language. We want to explicitly differentiate between sequential and parallel programming languages. Therefore, we define a *sequential programming language* as a language that does not include intertask synchronization or communication statements. In contrast, we define a *parallel programming language* as a language that contains explicit inter-task synchronization or communication statements.

The outcome of a comparison with related approaches is that we see three key differentiators, between our approach and related approaches. The first differentiator is that we can always analyze the data dependencies in OIL, also for non-manifest state-

Figure 2.1: Overview of a parallelization approach

ments, such that only the data dependencies will determine the execution order of the tasks. Our second differentiator is that we introduce a new buffer type that can always be inserted to replace the communication via an array. The third differentiator is the underlying temporal analysis model for our parallelization approach, which is used to reduce the synchronization overhead and to compute sufficient buffer sizes, such that temporal constraints are satisfied.

Though this chapter will highlight the differences between our automatic parallelization approach and related approaches, we recognize the value of the related approaches.

For this chapter, the outline is as follows. First, Section 2.1 discusses the sequential programming languages. In section 2.2, we discuss related parallelization tools. We will discuss the parallel programming languages that can be used for a task graph that is extracted by a parallelization approach, in Section 2.3. The underlying temporal analysis models that are suitable for a parallelization approach are discussed, in Section 2.4. Finally, Section 2.5 presents the conclusions.

# 2.1 Sequential programming languages

The sequential programming language that is used to describe the input application of an automatic parallelization tool determines the parallelism that this tool can extract. Essential for the extraction of parallelism is the dependency analysis. If data dependencies can be derived, then they can be used to specify the execution order between the assignment-statements that should at least be maintained. Our requirements for a sequential programming language are that it supports non-manifest loops and if-statements, that the data dependencies are explicit, and that the data dependencies can be derived. This should result in a language in which it is transparent for the programmer which assignment-statements will be executed in parallel. If the data dependencies can be derived, the execution order of the tasks in the task graph will only be determined by these dependencies.

For the discussion of related sequential programming languages, we will try to classify them. Therefore, we will identify pure declarative languages, pure applicative languages, and pure imperative languages. We define a *pure declarative language* to only describe the logic of a computation, but not how the result should be computed. A *pure applicative language* is defined as a language in which the data dependencies between the assignment-statements are encoded, but not the execution order of the assignment-statements. In such a language, the data dependencies will determine the possible execution orders of the assignment-statements. We define a *pure imperative language* as a

language in which an explicit execution order of the assignment-statements is specified and the data dependencies are implicit.

DSWP [ORS+06], Cordes [CMM10], FP-MAP [KC97], and MAPS [CCS+08] extract parallelism from applications described in C. The C language contains a lot of elements from an imperative language, because C requires control-statements that describe an execution order for the assignment-statements in the application. Due to this explicit execution order, these languages can support non-manifest statements. But, the C language also contains elements from an applicative language, because it is possible to express data dependencies that can be derived by these parallelization approaches. However, since the semantics of the C language do not enforce the data dependencies to be explicit, the dependency analysis is not always successful. If the data dependencies cannot be derived, certain statements may not be executed in parallel, to prevent incorrect functional behavior.

In addition to the approaches in the previous paragraph, Sprint [CDVS07] extracts parallelism from applications described in the C language that are annotated with pragmas to indicate parallelization points. Adding pragmas to the C language results in a language that contains elements from an applicative language. These pragmas indicate points at which data dependencies can be derived that might not have been automatically identified by the parallelization approach.

The language Compel [TE68] is an applicative language. The execution order of the statements is only determined by the data dependencies, which are explicit, such that they can always be extracted. The data dependencies can completely determine the execution order, because Compel is a SA language. For an application written in a SA language, during the lifetime of a variable, the variable is assigned a value only once. Therefore, no additional dependencies are required to prevent values from being overwritten. However, because this language does not contain control-statements, it is difficult to describe the behavior of stream processing applications that have non-manifest statements.

The Sil [KvMN<sup>+</sup>92] and Silage [HRG<sup>+</sup>90, VSR96] languages contain a lot of elements from an applicative language. In these languages, an application is described by a directed graph that describes the dependencies between the functions. The power of these languages is that they are SA languages, such that the parallel execution of the statements is completely determined by the data dependencies. In addition to Compel, these languages do support a form of control-statements, such that they contain some imperative elements. Therefore, it may be possible to express stream processing applications using these languages.

The Compaan/PN [Tur07, VNS07, Ste04, NNS10] and Phideo [LvMvdW<sup>+</sup>91] parallelization approaches require an application in the form of an affine NLP as input. An affine NLP is described in a language in which assignment-statements can be nested in for-loops with manifest bounds, where the extensions in [Ste04, NNS10] also support non-manifest if-statements and for-loops with non-manifest bounds. The assignment-statements in the NLPs may access arrays, but must use affine index-expressions. The control-flow determines the execution order of an assignment-statement, which is an element from an imperative language. An element from an applicative language is that all data dependencies can be derived between the accesses of array elements, due to the

affine index-expressions and the supported loops. Because all data dependencies can be analyzed, these approaches can transform the affine NLPs into SA form, which is an essential step for these approaches. In this transformed NLP, the execution order between assignment-statements will only be determined by the data dependencies. However, the non-manifest behavior of our stream processing applications cannot be expressed in this language.

In this thesis, we introduce a new language to describe stream processing applications. Our language OIL contains aspects from an imperative language, because an application may contain assignment-statements nested in non-manifest loops or if-statements. An application described in OIL contains assignment-statements nested in loops and ifstatements, such that initially at least a valid execution order of the assignment-statements is specified that will certainly not result in deadlock for the application. An applicative aspect of OIL is that we can always extract data dependencies. For non-manifest statements, we can at least extract approximated data dependencies [BCF97] between accesses of arrays, whereas for manifest statements we can extract data dependencies between the accesses of array elements. Between assignment-statements, the execution order is only determined by the data dependencies, because we require an application to be described in our own SA form. Though some approaches consider the transformation into SA form as an essential step, we did not encounter problems while describing our stream processing applications in our own SA form. Because we can always analyze the data dependencies and only these dependencies determine the execution order between assignment-statements, we can always extract function parallelism.

#### 2.2 Parallelization tools

Automatic parallelization is performed in the front-end of a multiprocessor compiler and extracts a task graph described in a parallel programming language from an application described in a sequential programming language. The first step is the identification of tasks in the sequential programming language and the extraction of dependencies between these tasks, which results in a dependency graph. Next, the dependencies are replaced by inserting inter-task communication and synchronization statements into the tasks, such that we get a task graph from which the tasks can be executed in parallel on a multiprocessor system. Our requirement for a parallelization tool is that it can automatically extract all function parallelism from an input application that may contain non-manifest loops and if-statements, where the execution order of the tasks will only be determined by the extracted data dependencies.

In this section, we will first examine parallelization tools that extract *data parallelism* and subsequently we will examine tools that extract *function parallelism*. With the discussions in this section, we want to emphasize the possibility of our parallelization tool to extract function parallelism from stream processing applications, as claimed in contribution 1.

**Data parallelism** The approaches presented in [Ban94, Bas03, CG06, Fea96, WL91] can be applied to extract data parallelism from affine NLPs. They require affine index-

expressions in an NLP, such that all data dependencies for the array accesses can be captured in the polyhedral model [Fea91, Pug94, PW94]. The goal of these approaches is to minimize the dependencies between loop iterations, such that each iteration can be assigned to a different task. Using the polyhedral model, they can compute transformations for the data dependencies in an NLP, amongst others to maintain only data dependencies between the iterations of the outer-most loop. If this is possible, there is only synchronization between the iterations of the outer-most loop, such that the iterations of nested loops can be executed in parallel.

Extensions to the approaches in the previous paragraph have been proposed, such that data parallelism can be extracted from while loops. In [LG95], depending on the dependencies in the loop nest, it may be possible to transform the loops in the NLP, such that the while loop becomes the outer most loop, for which the iterations can be executed in parallel. Collard [Col95] extends this approach, by allowing speculative executions of while loop iterations, where an unnecessary executed loop iteration can be undone. Both approaches require affine index-expressions, such that they can capture the dependencies in the polyhedral model.

In [RP95] an approach is presented to extract data parallelism from non-manifest loops, for which speculative execution of loop iterations is performed, without requiring affine expressions. But, this approach does not perform transformations to the loop nest, instead it only determines if the dependencies allow iterations to be executed in parallel.

The tools presented by Franke [FO05] and Meijer [MKTdK07] can be used to extract data parallelism from affine NLPs with manifest loops, such that the data dependencies can be captured in the polyhedral model, with which transformations for the loop nests can be computed. In addition, Franke inserts *barrier statements* [CGS99] into the tasks for the inter-task synchronization. One barrier is used for the synchronization of multiple tasks. If a task executes a barrier statement, it is blocked until the other tasks that synchronize on this barrier executed their barrier statement. Meijer inserts FIFO buffers for the data dependencies between iterations.

For stream processing applications, it is often not possible to extract iterations without dependencies, which may limit the amount of data parallelism that can be extracted. Furthermore, stream processing applications often contain non-manifest statements for which the dependencies cannot be captured in the polyhedral model, such that only a limited number of transformations can be applied to increase the available data parallelism. Nonetheless, we see the extraction of data parallelism from stream processing applications as interesting future work.

The description of a stream processing application from the channel decoding or video processing domain often indicates a functional partitioning [Wal91, IEE07, SP09] that already expresses the pipeline to process an endless stream of input values. Such a functional partitioning implicitly specifies the available function parallelism. The extracting of function parallelism fits well with these applications, because each function can be assigned to a separate processor to construct the pipeline to process the endless stream of input values. Therefore, the remainder of this section will focus on tools to extract function parallelism.

**Function parallelism** Sprint [CDVS07] extracts function parallelism from C-code. *Pragmas* are used to indicate the potential parallelization points. Sprint inserts FIFO buffers for the inter-task communication. They can identify the reordering and buffers selection problems, but require the user to manually solve them by inserting synchronization statements and shared memory communication.

Thies [TCA07] presents an approach to pipeline the execution of C-code. This approach requires the user to insert pragmas into the code and restricts the pipelining to the outermost loop in the code, where the dependencies must be acyclic. Between the different stages of the pipeline, all shared values are copied in FIFO order.

Sprint and the approach presented by Thies require the user to indicate the parallelization points, because they cannot always derive the data dependencies. We think that it is desirable that the parallelization tool can derive the data dependencies in the sequential programming language, such that the parallelism can be extracted automatically.

FP-MAP [KC97] and MAPS [CCS+08] extract function parallelism from C-code. Based upon a dependency analysis, assignment-statements are assigned to tasks. FP-MAP does not insert inter-task synchronization statements into the tasks. MAPS inserts FIFO buffers for the inter-task communication, but cannot solve the reordering and buffer selection problems, such that this may limit the amount of extracted function parallelism.

DSWP [ORS+06] and Cordes [CMM10] extract function parallelism from C-code inspired by software pipelining. Based on the control-flow and the data dependencies, basic blocks [ALSU06] are identified in the C-code. These blocks can be executed in parallel and for the dependencies between the basic blocks, barrier synchronization is inserted. But, the dependencies between the basic blocks are not only determined by the data dependencies, but also by sequence dependencies due to the control-flow of an application. Therefore, the extracted function parallelism may be limited.

Compel [TE68], Sil [KvMN<sup>+</sup>92], Silage [HRG<sup>+</sup>90, VSR96], and Sisal [FCO90, GSH88] are applicative languages. One of the main goals of these languages is the extraction of function parallelism. These languages are single assignment (SA) languages [TE68] from which all data dependencies can be derived, such that all function parallelism can be extracted. However, the compilers for these languages do not insert inter-task communication and synchronization statements. Instead, they compute a valid execution order for the tasks at compile time. At run-time, this execution order should be enforced by a central scheduling unit. In contrast, using synchronization statements inside the tasks does not enforce a single execution order and does not require a central scheduling unit, which can become a bottleneck in current multiprocessor systems.

The Compaan/PN parallelization tools [Tur07, VNS07] can extract parallelism from affine NLPs. Due to the affine index-expressions and the manifest loops, data dependencies can be extracted. Using the data dependencies, a task graph can be extracted in which the array accesses are replaced by inter-task communication via FIFO buffers. Solutions have been presented to solve the reordering and buffer selection problems [TKD04b, TKD02], but these are only applicable for affine index-expressions and manifest loops and if-statements.

CompaanDyn [SD03] is an extension of the Compaan/PN parallelization tools that supports non-manifest if-statements. A task extracted from an assignment-statement that

is nested in a non-manifest if-statement has to perform inter-task communication via a special FIFO buffer. For this FIFO buffer, a special controller is added to the producer and the consumer of the buffer. At compile time, these controllers are configured by computing a valid execution order of the tasks that communicate via the FIFO buffer. Therefore, the execution of the tasks is not only determined by the data dependencies, but also by sequence dependencies, due to non-manifest if-statements. Furthermore, CompaanDyn still does not support non-manifest loops.

While this thesis was written, the CompaanDyn approach has been extended to support weakly dynamic NLPs with non-manifest for-loops [NNS10]. These for-loops may contain a non-manifest upper or lower bound. However, this extension does still not support non-manifest while-loops and non-affine index-expressions. After publishing the draft version of this thesis we were told that the PN tool supports stream processing applications with an endless loop, however how these loops are supported has not been published. Because the CompaanDyn approach provides a solution for only a part of the problems addressed in this thesis, it is not possible to give a fair comparison of the results of this approach and the results of the approach presented in this thesis.

Our automatic parallelization tool Omphale can extract function parallelism from stream processing applications that may contain non-manifest statements. From applications described in OIL we can at least extract approximated data dependencies [BCF97]. Using these data dependencies, we can replace the array accesses by inter-task communication and synchronization via one of our new buffer types. Because we use the data dependencies to insert the inter-task synchronization, only the data dependencies determine the execution order of the tasks. Furthermore, if we use the new buffer type that is suitable for latency critical cycles, a value that has been written into this buffer is immediately available for reading, such that maximum function parallelism is extracted.

# 2.3 Parallel programming languages

In this section, we will discuss parallel programming languages. These languages contain inter-task communication and synchronization statements, such that they are suitable to describe a task graph that has to be executed on a multiprocessor system. The requirement that we have for a parallel programming language is that it contains communication and synchronization calls that are rich enough, such that we can circumvent the buffer selection and reordering problems.

Examples of parallel programming languages are Cilk++ [Lei09], MPI [Mes03], OpenMP [DM98, Ope08], Pthreads [Pth96], StreamIt [DHRA06], and the language proposed by Reid et al. [RFGEL08]. In these languages, the user explicitly indicates the parallelism in an application by inserting pragmas for the potential parallelization points. Furthermore, data dependencies should be encoded by inserting synchronization statements. In these languages, both data and function parallelism can be expressed. In Cilk++, MPI, and OpenMP the amount of extracted data parallelism can be determined at runtime, depending on the current workload of the system. A brief overview of these approaches can be found in [DM98, MHT<sup>+</sup>10].

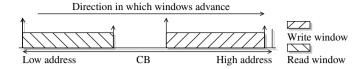

To express function parallelism in Cilk++, MPI, OpenMP, Pthreads, StreamIt, or the language proposed by Reid et al., the user has to insert inter-task synchronization statements for the shared variables. In addition, if the execution of the tasks has to be pipelined, the user has to insert special inter-task communication statements to encode the pipelined execution of the tasks and compute the size of the used buffers manually. These languages do not provide synchronization and communication calls to use so called read and write windows of which you can have an arbitrary number in a buffer, such that the user has to solve the buffer selection problem.

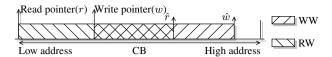

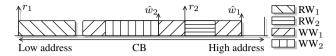

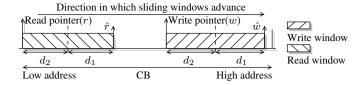

The synchronization and communication statements that are called by the tasks in a task graph can be specified by an application programming interface (API) that is implemented by a streaming library, as e.g. TTL [vdWdKH+04], which includes the interfaces specified in [dKSvdW+00, NKG+02, RvEP02]. By using such an API in a sequential programming language, according to our definition, it becomes a parallel programming language. The API of TTL provides synchronization statements to the user, such that a buffer with a sliding read and write window can be used. Such a window contains a number of consecutive locations that can be accessed in an arbitrary order. But, the TTL API only supports that all locations in a window are either available for reading or writing. For a cyclic task graph this may cause deadlock, as we will show in Section 5.3.3. Furthermore, TTL does not support multiple producers, such that it does not avoid the buffer selection problem.

The approach for inter-task communication proposed in [HGT07] uses *containers* for the inter-task communication, where a container is a place holder for values. Inside a container, locations can be accessed in any order and therefore a reordering task is not required. After values are written in a container, the container is released such that the consumer can read from it. But, released containers have to be read in FIFO order, such that there is no reordering between released containers. Furthermore, this approach only allows complete containers to be released and therefore a container should not be released before the values in the container have been written.

Parallel programming using one of the discussed parallel programming languages requires the user to manually partition the application and to explicitly define the synchronization that has to be performed. This allows the user to apply some optimizations to the task graph. However, the drawback is that the user is often responsible for the insertion of synchronization for shared variables, where incorrect synchronization may lead to hard to debug race-conditions [AB09, Lee06]. Therefore, we chose to perform automatic parallelization, starting from an application described in a sequential programming language.

The presented parallel programming languages and APIs provide inter-task communication and synchronization statements that cannot be used in a straightforward way to avoid the buffer selection problem. Furthermore, these approaches do not provide synchronization statements to overlap multiple read and write windows, such that deadlock may be introduced for cyclic task graphs. Therefore, we introduce a new buffer type with associated inter-task communication and synchronization statements. This buffer type avoids the reordering and buffer selection problems and can be applied for latency

critical data dependencies. In Section 5.4, we will prove that this buffer type can always be inserted to replace the array communication in an application that is described in OIL.

# 2.4 Temporal analysis models

In this section, we will focus on the underlying temporal analysis model for our parallelization approach, which we claimed to have for our approach in contribution 3. We will discuss two possible underlying temporal analysis models that can be used to guarantee the satisfaction of a throughput constraint for a stream processing application. Next, available approaches to extract an analysis model from a parallel programming language are examined.

Analysis models The synchronous languages Signal, Lustre, and Esterel have an underlying analysis model [BCE<sup>+</sup>03]. But, the goal of the underlying analysis model is not the verification of a throughput constraint, instead they require the model to reason formally about the functional behavior of their stream processing applications.

The analysis models known to us that can be used to guarantee a throughput constraint are the real-time calculus [TCN00] and dataflow analysis [Wig09] models. The real-time calculus analysis model can be used to provide guarantees on the throughput constraint and buffer capacities for a stream processing application that will be executed on a multiprocessor system. We define a buffer capacity as the number of locations available in a buffer. Input to the real-time calculus approach is a characterization of the executions of the tasks in the task graph, which requires worst-case and best-case execution times for the tasks. However, this analysis technique is currently less suitable for cyclic task graphs, whereas we target applications that may have a cyclic task graph. An example of such a cyclic task graph is given in Figure 1.1.

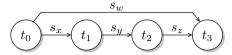

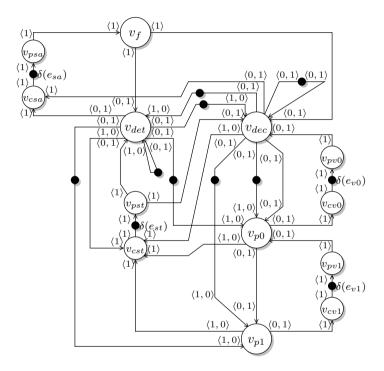

We chose to use a *dataflow analysis model* as an underlying analysis model of our automatic parallelization approach, because it supports cycles in the analysis model. The cyclo static dataflow (CSDF) model is suitable to model periodic synchronization behavior between tasks via their buffers, even for cyclic task graphs. In addition, the CSDF model also enables our automatic parallelization tool to perform optimizations, for example by computing a buffer capacity that may be smaller than the communicated array, by selecting synchronization calls that can be combined [HBC11], or by selecting the buffer type to be inserted [Geu10]. Note that these optimizations use the required throughput as a constraint.

Analysis model extraction Several approaches address the extraction of an analysis model from a task graph. In [HT07, HKH+09], the extraction of a real-time calculus analysis model from a task graph is presented. They consider applications that only contain FIFO buffers for the inter-task communication. The buffer capacities and other parameters of the system are required before the real-time calculus model can be used to verify if the application will meet its throughput constraint. Furthermore, the used analysis model restricts the task graphs to be acyclic.

In addition to the Compaan/PN approach, Meijer proposes to model a task graph using a dataflow model [MNS10]. With the dataflow model, the throughput of a task graph

is analyzed and tasks that can be merged are selected. This approach is only capable to extract a dataflow model from an acyclic task graph in which tasks communicate via FIFO buffers.

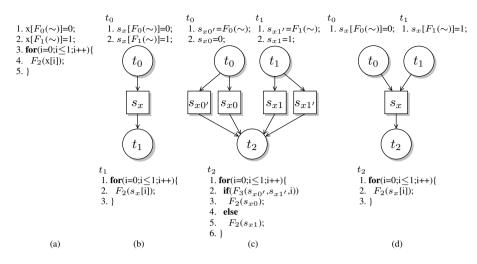

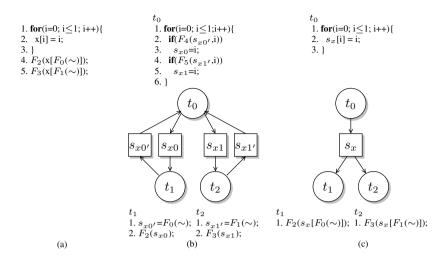

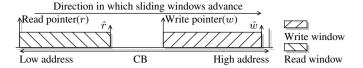

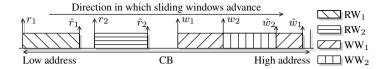

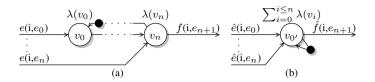

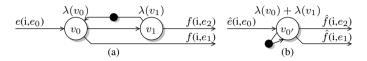

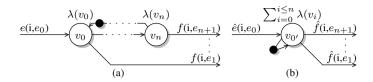

The extraction of a CSDF model from tasks that perform inter-task communication via buffers with sliding windows is presented in [DBC<sup>+</sup>07]. This approach discusses the extraction of a CSDF model from a sliding read and write window in a buffer and also presents a modeling technique to model multiple sliding read windows and one sliding write window in a buffer. But, this paper only focuses at a single buffer and therefore does not discuss the extraction of a CSDF model from the inter-task communication in a task graph.